Faculty of Science and Technology Department of Computer Science

## **ROPE: Reducing the Omni-kernel Power Expenses**

Implementing power management in the Omni-kernel architecture

Jan-Ove A. Karlberg

INF-3990 Master thesis in Computer Science, May 2014

"That's it man, game over man, game over!

What the fuck are we gonna do now?

What are we gonna do?"

-Hudson, Aliens (1986)

## **Abstract**

Over the last decade, power consumption and energy efficiency have arisen as important performance metrics for data center computing systems hosting cloud services. The incentives for reducing power consumption are several, and often span economic, technological, and environmental dimensions. Because of the vast number of computers currently employed in data centers, the economy of scale dictates that even small reductions in power expenditure on machine level can amount to large energy savings on data center scale.

Clouds commonly employ hardware virtualization technologies to allow for higher degrees of utilization of the physical hardware. The workloads encapsulated by virtual machines constantly compete for the available physical hardware resources of their host machines. To prevent execution of one workload from seizing resources that are intended for another, absolute visibility and opportunity for resource allocation is necessary. The Omni-kernel architecture is a novel operating system architecture especially designed for pervasive monitoring and scheduling. Vortex is an experimental implementation this architecture.

This thesis describes ROPE (Reducing the Omni-kernel Power Expenses), which introduces power management functionality to the Vortex implementation of the Omni-kernel architecture. ROPE reduces the power consumption of Vortex, and does so while limiting performance degradation.

We evaluate the energy savings and performance impacts of deploying ROPE using both custom tailored and industry standard benchmarks. We also discuss the implications of the Omni-kernel architecture with regards to power management, and how energy efficiency can be accommodated in this architecture.

# **Acknowledgements**

I would like to thank my supervisor, Dr. Åge Kvalnes for his great advice, ideas, and highly valued input throughout this project. Your passion and knowledge is unmatched. The realization of this project would not have been possible without you.

Further I would like to thank Robert Pettersen for his invaluable help. Your incredible insight into the Omni-kernel architecture project has been a life-saver in many a situation. Many thanks for putting up with all my requests for new convenience tools.

I would also like to thank some of my fellow students whose help have been crucial throughout this project. In no particular order: Kristian Elsebø, thank you so much for all help with diskless servers, HammerDB, and general sysadmin stuff. Erlend Graff, your knowledge, kindness, and enthusiasm is simply incredible. Only he who has seen the red zone can understand my gratitude. Einar Holsbø, my harshest literary critic: thank you so much for your valued advice, and for proof-reading this entire text. To all of the above, and all the rest of you whose names are to many to list here: Thank you so much, I am truly blessed to be able to call you my friends.

To my family, parents and brothers: without your continuous support none of this would have been possible.

Finally, to my girlfriend Martine Espeseth. Thank you so much for all your love and support. Especially through the last month's coffee fueled frenzy.

# **Contents**

| Ał | ostrac | <b>et</b> i                          | ii  |

|----|--------|--------------------------------------|-----|

| Ac | knov   | vledgements                          | v   |

| Li | st of  | Figures                              | хi  |

| Li | st of  | Tables xi                            | iii |

| Li | st of  | Listings                             | v   |

| Li | st of  | Abbreviations xv                     | ii  |

| 1  | Intr   | oduction                             | 1   |

|    | 1.1    | Problem Definition                   | 3   |

|    | 1.2    | Scope and Limitations                | 3   |

|    | 1.3    | Interpretation                       | 4   |

|    | 1.4    | Methodology                          | 4   |

|    | 1.5    | Context                              | 5   |

|    | 1.6    | Outline                              | 5   |

| 2  | Pow    | ver Management                       | 7   |

|    | 2.1    | Introduction to Power Management     | 7   |

|    | 2.2    | Evaluating Power Management Policies | 8   |

|    | 2.3    | Approaches to Power Management       | 0   |

|    |        | 8                                    | .1  |

|    |        |                                      | 2   |

|    |        | o o                                  | 2   |

|    | 2.4    | 8                                    | 4   |

|    |        |                                      | 4   |

|    |        |                                      | .5  |

|    |        | 2.4.3 Power Management of CPUs       | .5  |

| 3  | ROF    | PE Architecture and Design 1         | 7   |

|    | 2 1    | RODE Dower Management Architecture   | 7   |

viii CONTENTS

|   | 3.2 | Design  | n                                        | 18         |

|---|-----|---------|------------------------------------------|------------|

|   |     | 3.2.1   | CPU Core Power State Management          | 20         |

|   |     | 3.2.2   | CPU Core Performance State Management    | 22         |

|   |     | 3.2.3   |                                          | 23         |

|   |     |         |                                          |            |

| 4 | _   | lement  |                                          | <b>2</b> 7 |

|   | 4.1 | ACPI    |                                          | 27         |

|   |     | 4.1.1   | F I                                      | 28         |

|   |     | 4.1.2   |                                          | 29         |

|   | 4.2 | Intel S | Specific Advanced Power Management       | 32         |

|   |     | 4.2.1   |                                          | 33         |

|   |     | 4.2.2   | The MONITOR/MWAIT Instruction Pair       | 33         |

|   | 4.3 | The S   | hare Algorithm                           | 34         |

|   |     | 4.3.1   | Definition                               | 35         |

|   | 4.4 | Per-co  | ore Power State Management               | 37         |

|   |     | 4.4.1   | Aggressive Entry of C-states             | 37         |

|   |     | 4.4.2   | J                                        | 37         |

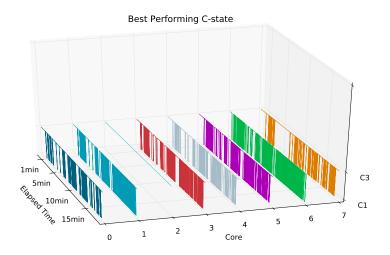

|   |     | 4.4.3   | Select Best Performing C-state           | 40         |

|   | 4.5 | Per-co  | ore Performance State Management         | 49         |

|   |     | 4.5.1   | Quantifying CPU Utilization              | 50         |

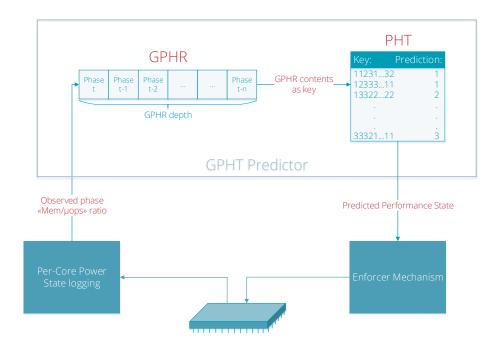

|   |     | 4.5.2   | Global Phase History Table Predictor     | 50         |

|   |     | 4.5.3   | Naive Forecaster                         | 57         |

|   | 4.6 | Energ   | y Efficient Scheduling                   | 58         |

|   |     | 4.6.1   | Topology Agnostic Dynamic Round-Robin    | 59         |

| _ |     |         |                                          |            |

| 5 |     | luation |                                          | 63         |

|   | 5.1 |         | odology                                  | 63         |

|   |     | 5.1.1   | Experimental Platform                    | 64         |

|   |     | 5.1.2   | Measuring Power Consumption              | 64         |

|   |     | 5.1.3   | ApacheBench Workload Traces              | 65         |

|   |     | 5.1.4   |                                          | 66         |

|   |     | 5.1.5   |                                          | 66         |

|   |     | 5.1.6   | Fine Grained Workload                    | 67         |

|   | 5.2 |         | Power State Management                   | 68         |

|   |     | 5.2.1   | Aggressively Entering C-states           | 68         |

|   |     | 5.2.2   | Static Timeout Based C-state Entry       | 71         |

|   |     | 5.2.3   | Select Best Performing C-state           | 74         |

|   |     | 5.2.4   | Comparison of C-state Management Polices | 76         |

|   | 5.3 |         | Performance Management                   | 80         |

|   |     | 5.3.1   | GPHT Predictor                           | 80         |

|   |     | 5.3.2   | Comparison of Prediction Accuracy        | 80         |

|   |     | 5.3.3   | Comparison of P-state Management Polices | 84         |

|   | 5.4 | Core I  | Parking Scheduler                        | 86         |

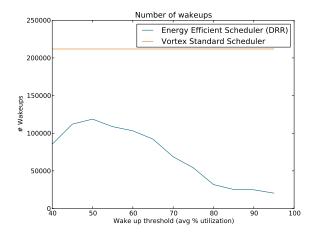

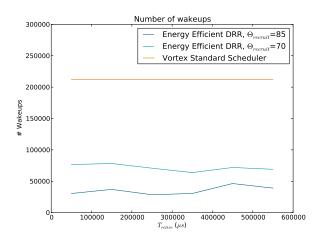

|   |     | 5.4.1   | Internal Measures                        | 87         |

CONTENTS ix

|     |            | 5.4.2 Comparison with Standard Vortex Scheduler 89             | 9 |

|-----|------------|----------------------------------------------------------------|---|

|     |            | 5.4.3 Effects of Energy Efficient Dynamic Round-Robin Schedul- |   |

|     |            | ing                                                            | C |

|     | 5.5        | Performance Comparison of Power Management Policies 93         | 3 |

|     |            | 5.5.1 Summary                                                  | 4 |

| 6   | Rela       | ited Work 95                                                   | 5 |

|     | 6.1        | Power Management of CPUs                                       | 5 |

|     |            | 6.1.1 Share Algorithm                                          | 5 |

|     | 6.2        | Energy Efficient Scheduling                                    |   |

|     | 6.3        | Power Management in Data Centers and Cloud 99                  | 9 |

|     | 6.4        | -                                                              |   |

| 7   | Dica       | ussion and Concluding Remarks 103                              | • |

| /   | 7.1        | Discussion                                                     |   |

|     | /.1        | 7.1.1 Findings                                                 |   |

|     |            | 7.1.2 Power Management in the Omni-kernel Architecture . 104   |   |

|     | 7.2        | Contributions and Achievements                                 |   |

|     | 7.2        | Future Work                                                    |   |

|     | 7.3<br>7.4 | Concluding Remarks                                             |   |

|     | , · ·      | Concluding remarks                                             | _ |

| Α   | ACP        | I Objects and Namespace 107                                    | 7 |

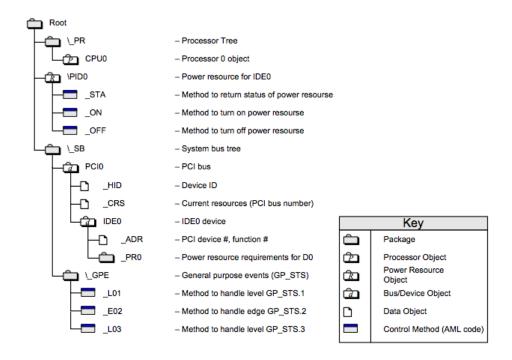

|     | A.1        | The ACPI Namespace                                             | 7 |

|     | A.2        | ACPI Objects                                                   | 3 |

|     |            | A.2.1 The OSC Object                                           | 3 |

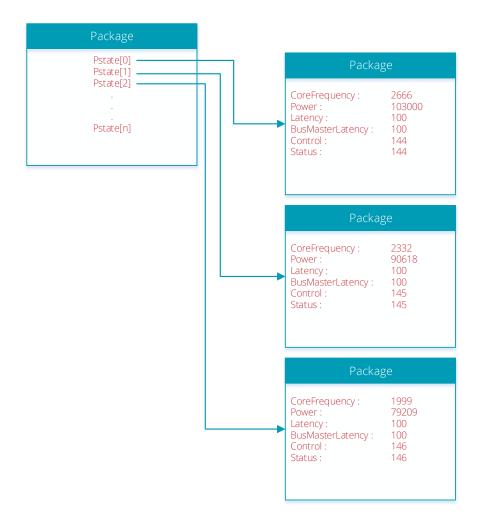

|     |            | A.2.2 The PSS Object                                           | 9 |

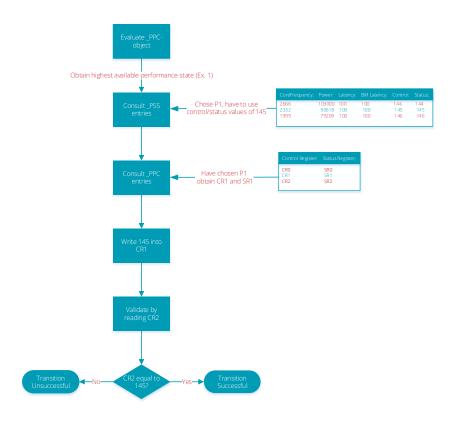

|     |            | A.2.3 The PPC Object                                           | 9 |

|     |            | A.2.4 The PCT Object                                           | 9 |

|     |            | A.2.5 The PSD Object                                           | 1 |

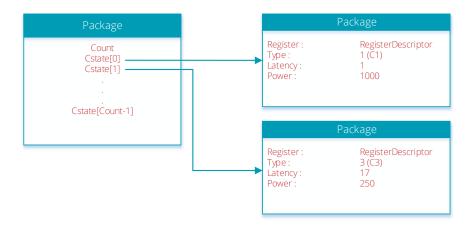

|     |            | A.2.6 The CST Object                                           | 2 |

| Bil | oliogi     | raphy 113                                                      | 3 |

|     | 0-         | -1 7                                                           | - |

# **List of Figures**

| 3.1  | Architecture of PM functionality implemented in Vortex              | 19 |

|------|---------------------------------------------------------------------|----|

| 3.2  | Design of a policy for aggressively entering C-states               | 21 |

| 3.3  | Design of policy for entering a C-state following a static timeout. | 21 |

| 3.4  | Design of policy dynamically selecting best C-state                 | 22 |

| 3.5  | Design of policy for managing CPU performance states                | 23 |

| 3.6  | Design of energy efficient scheduler                                | 25 |

| 4.1  | Architecture of ACPI                                                | 29 |

| 4.2  | Interaction between ACPICA-subsystem and host OS                    | 30 |

| 4.3  | Structure of ACPICA-subsystem                                       | 30 |

| 4.4  | Organization of CPU power-, performance-, and throttling            |    |

|      | states                                                              | 32 |

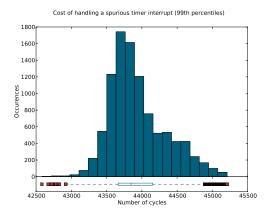

| 4.5  | Cost of handling spurious timer interrupt                           | 39 |

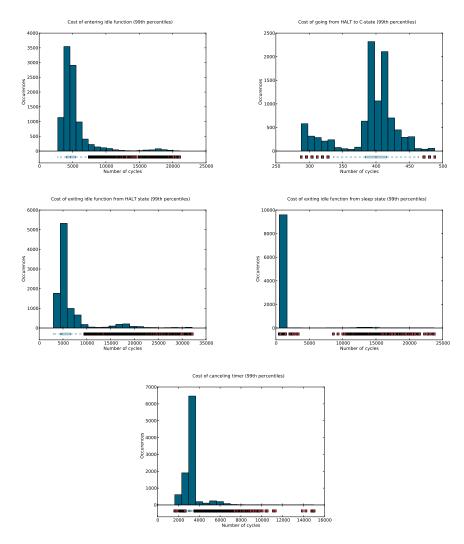

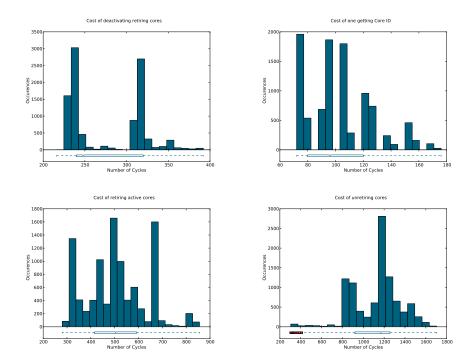

| 4.6  | Static Timeout Policy Overheads - Latency distributions             | 42 |

| 4.7  | Implementation of the policy selecting the best performing          |    |

|      | C-state.                                                            | 43 |

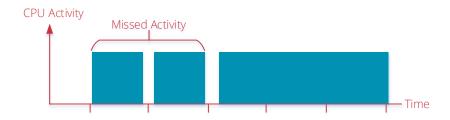

| 4.8  | Problem with periodic sampling of CPU activity                      | 44 |

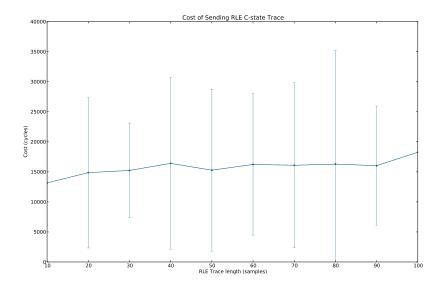

| 4.9  | Cost of sending RLE C-state trace                                   | 45 |

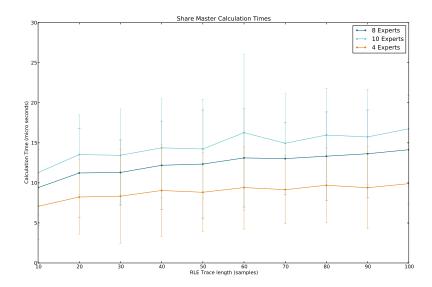

| 4.10 | Computational overhead of Share Algorithm                           | 47 |

| 4.11 | Selection of best performing C-state                                | 49 |

|      | Implementation of Core Performance State Manager                    | 52 |

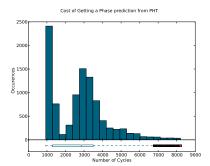

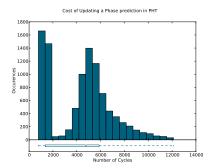

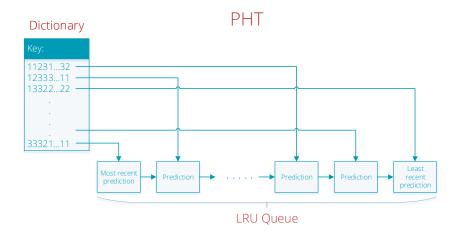

|      | PHT operation costs                                                 | 53 |

| 4.14 | Implementation of GPHT                                              | 55 |

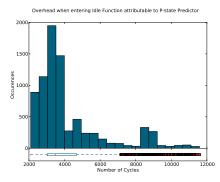

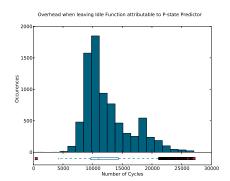

| 4.15 | Idle function overhead attributable to per-core performance         |    |

|      | management                                                          | 56 |

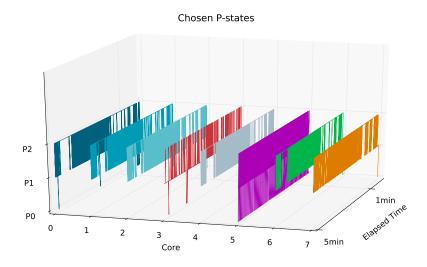

|      | Runtime selection of P-states                                       | 57 |

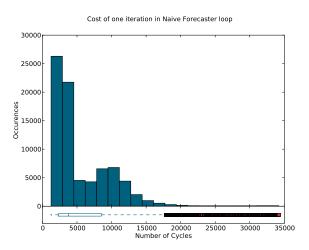

|      | Overhead of naive forecaster                                        | 59 |

|      | Implementation of energy efficient scheduler                        | 61 |

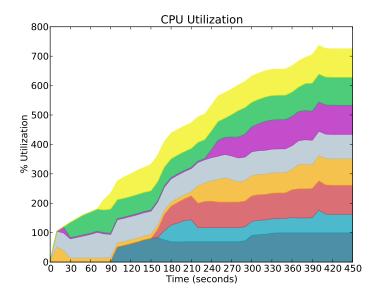

| 4.19 | CPU utilization over time under dynamic round-robin schedul-        |    |

|      | ing                                                                 | 61 |

| 4.20 | Energy efficient scheduling - Cost of operations                    | 62 |

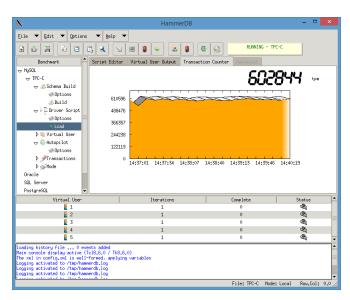

| 5.1  | Screenshot of running TPC-C with HammerDB                           | 67 |

| 5.2  | Power consumption of aggressively entering different C-states.      | 69 |

|      |                                                                     |    |

xii LIST OF FIGURES

| 5.3  | Summed latency of aggressively entering different C-states      | 70  |

|------|-----------------------------------------------------------------|-----|

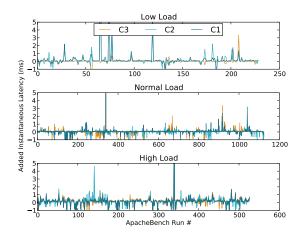

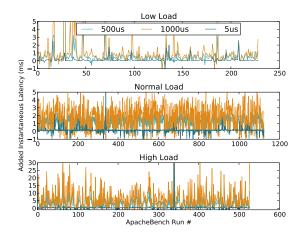

| 5.4  | Instantaneous Latency of aggressively entering different C-     |     |

|      | states                                                          | 71  |

| 5.5  | Power consumption of entering C-state following static timeout. | 72  |

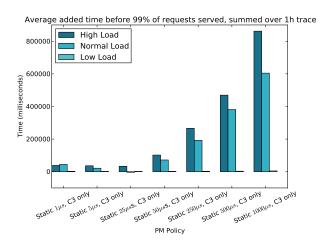

| 5.6  | Excess completion time resulting from entering C-state after    |     |

|      | static timeout                                                  | 73  |

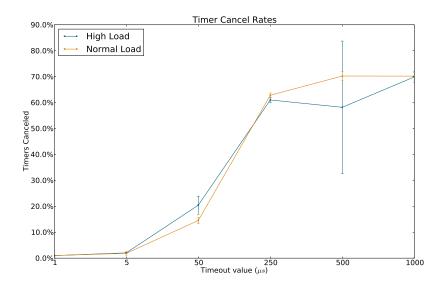

| 5.7  | Timer cancel rates for static timeout policies                  | 75  |

| 5.8  | User-perceived latency using static timeout policies            | 75  |

| 5.9  | Comparisons of Share Algorithm Configurations                   | 77  |

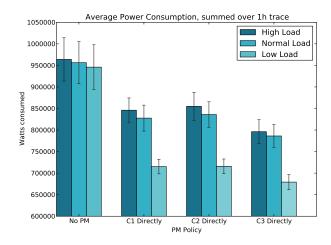

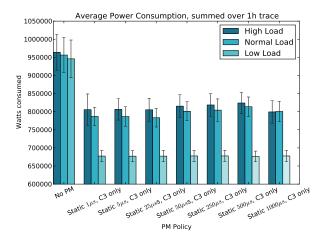

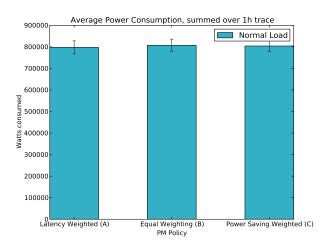

| 5.10 | Comparison of power consumption using different CPU C-          |     |

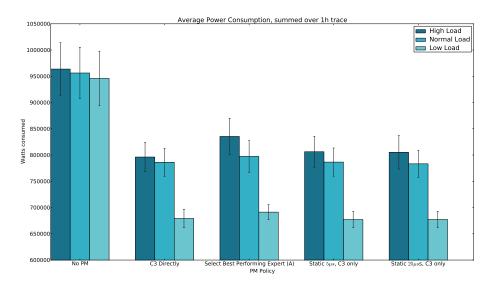

|      | state management policies                                       | 78  |

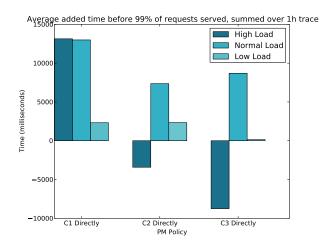

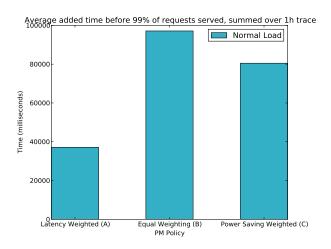

| 5.11 | Comparison of user experienced latency when employing dif-      |     |

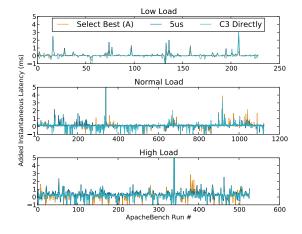

|      | ferent CPU C-state management policies                          | 79  |

| 5.12 | GPHT accuracy and hitrate                                       | 81  |

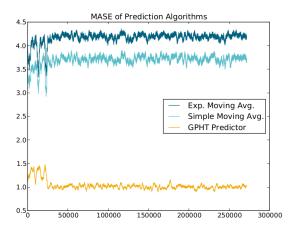

| 5.13 | MASE of different prediction algorithms                         | 83  |

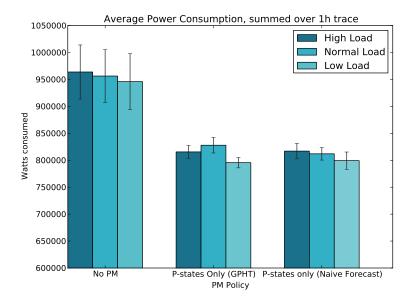

| 5.14 | Power consumption of using only P-states                        | 85  |

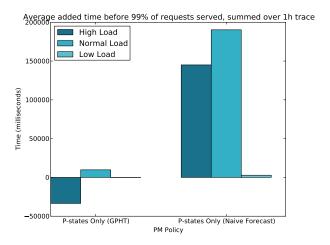

| 5.15 | Excess completion times using P-states for power management.    | 85  |

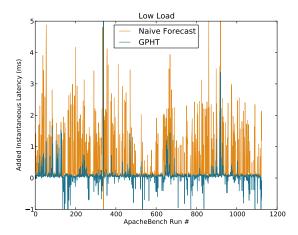

| 5.16 | Instantaneous latency of using P-states for power management.   | 86  |

| 5.17 | Properties of energy efficient DRR scheduler                    | 88  |

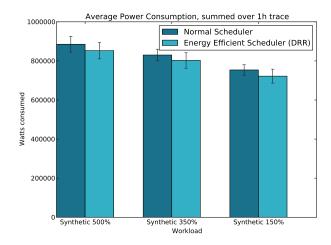

| 5.18 | Power consumption of synthetic loads using energy efficient     |     |

|      | DRR scheduler                                                   | 89  |

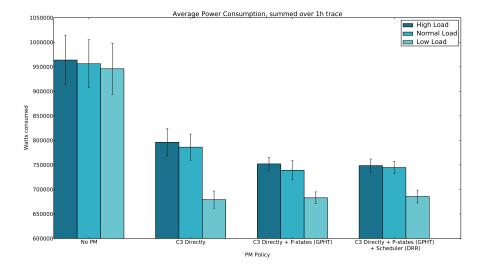

| 5.19 | Comparison of power consumption using different CPU PM          |     |

|      | policies                                                        | 90  |

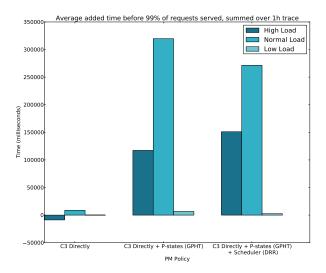

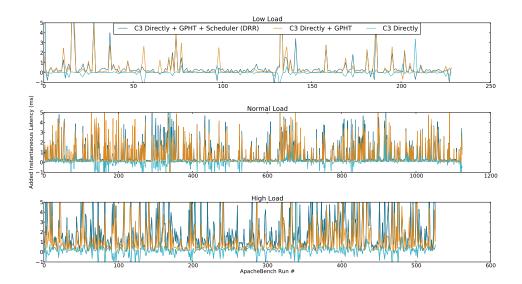

| 5.20 | Excess completion time resulting from use of PM policy com-     |     |

|      | binations                                                       | 91  |

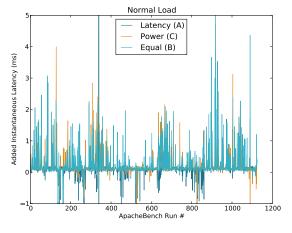

| 5.21 | User-perceived latency using PM policy combinations             | 92  |

|      |                                                                 |     |

| A.1  | ACPI namespace object                                           | .08 |

| A.2  | Evaluation of _PSS object                                       |     |

| A.3  | Entering of CPU P-state                                         |     |

| A.4  | Evaluation of _CST object                                       | 12  |

# **List of Tables**

| 4.1                   | "mem/ $\mu$ -ops" to execution phase mappings                  | 51 |

|-----------------------|----------------------------------------------------------------|----|

| 4.2                   | Summary of Core Performance Management Implementation          |    |

|                       | costs                                                          | 57 |

|                       |                                                                |    |

| 5.1                   | Summary of AB workload trace generation                        | 66 |

| 5.2                   | Workload relative energy savings when entering C-states di-    |    |

|                       | rectly                                                         | 69 |

| 5.3                   | Summary of performance degradation due to direct entry of      |    |

|                       | C-states                                                       | 71 |

| 5.4                   | Summary of performance degradation due to entering C-state     |    |

|                       | following a static timeout                                     | 74 |

| 5.5                   | Share Master Configurations                                    | 76 |

| 5.6                   | Summary of performance of Share Algorithm with different       |    |

|                       | configurations                                                 | 76 |

| 5.7                   | Comparison of C-state management policies                      | 79 |

| 5.8                   | Accuracy of implemented P-state prediction algorithms          | 82 |

| 5.9                   | Accuracy and MASE of P-state prediction algorithms             | 84 |

| 5.10                  | Comparison of P-state management policies                      | 84 |

|                       | Relative energy saving when using energy efficient DRR sched-  |    |

|                       | uler                                                           | 90 |

| 5.12                  | Comparison of ROPE PM policies                                 | 92 |

|                       | Summary of TPC-C performance for various PM algorithms.        | 94 |

| $\sigma$ . I $\sigma$ | ballinary of it o o periorinaries for various rivi argorithms. |    |

# **List of Listings**

| 4.1 | Usage of MONITOR/MWAIT instruction pair                             | 35 |

|-----|---------------------------------------------------------------------|----|

| 4.2 | Idle function accommodating aggressive entry of C-states            | 38 |

| 4.3 | Idle function with code for entering C-states after static timeout. | 41 |

| 4.4 | Idle loop modified to support entry of best performing C-state.     | 48 |

| 4.5 | Idle function modified to support P-state selection                 | 54 |

| 4.6 | Performance State Management Thread                                 | 56 |

| 4.7 | Naive Forecaster                                                    | 58 |

# **List of Abbreviations**

$\mu$ -ops micro-ops

AB ApacheBench

ABI application binary interface

**ACPI** Advanced Configuration and Power Interface

**ACPICA** ACPI Component Architecture

AML ACPI Machine Language

APM advanced power management

**CDN** content delivery network

**CMOS** Complementary metal-oxide-semiconductor

**CPU** central processor unit

**CPUID** cpu Identification

**DC** data center

**DPM** dynamic power management

DRR dynamic round-robin

**DVFS** dynamic voltage and frequency scaling

**DVS** dynamic voltage scaling

**EM** enforcement mechanism

EMA exponential moving average

**FFH** functional fixed hardware

**GPHR** Global Phase History Register

**GPHT** Global Phase History Table

**HTTP** HyperText Transfer Protocol

I/O input/output

ICT information and communication technologies

IPMI Intelligent Platform Management Interface

**LKM** loadable kernel module

LLC last-level cache

**LRU** least recently used

MASE mean absolute scaled error

**MWAIT** Monitor Wait

**NOPM** new-order transactions per minute

**OKA** omni-kernel architecture

**OLTP** online transaction processing

**OS** operating system

**OSL** OS Service Layer

**OSPM** Operating System-directed Power Management

**PCI** Periperhal Component Interconnect

**PCIe** Peripheral Component Interconnect Express

PHT Pattern History Table

List of Abbreviations xix

**PM** power management

**PMC** performance monitoring counter

**PMI** performance monitoring interrupt

**PSM** Policy State Manager

Qos quality of service

**RLE** run-length encoding

**ROPE** Reducing the Omni-kernel Power Expenses

SLA service level agreement

**SLO** service level objective

**SMA** simple moving average

**soc** system on chip

**TPC** Transaction Processing Performance Council

TPM transactions per minute

**URL** Uniform Resource Locator

**VFI** voltage/frequency island

**VLAN** Virtual LAN

VM virtual machine

VMM virtual machine monitor

**VPC** Virtual Private Cloud

WLAN wireless local area network

# /1

# Introduction

Over the last decade, power consumption and energy efficiency have arisen as important performance metrics for data center (DC) computing systems hosting cloud services. The incentives for reducing power consumption are several, and often span economic, technological, environmental, and even political dimensions. Already in the mid nineties, the concept of "green computers" surfaced as a response to increased CO<sub>2</sub> emissions and growing costs [85]. Emissions and costs have only increased with time, and in 2007, the information and communication technologies (ICT) sector was estimated to have been responsible for approximately 2% of all global carbon emissions, 14% of this being attributable to data center operation [87]. In 2012, Facebook's DCs alone had a carbon footprint of 298 000 tons of CO<sub>2</sub> [8], roughly the same as emissions originating from the electricity use of 24 000 homes [1].

Emissions originating from DCs are expected to double by 2020 [87]. Thus, DC energy consumption is no longer only a business concern, but also a national energy security and policy concern [90]. For example, in the United States, the U.S. Congress is taking the issue of DC energy efficiency to the national level [4]. Equivalently, the European Commission is considering the introduction of a voluntary code of conduct regarding energy efficiency in DCs [5]. It is expected that other regions and countries will introduce similar regulations and legislation within the foreseeable future [90].

Technologically, reducing power consumption is important mainly for two reasons. First, high power consumption is directly correlated with increased heat

dissipation. As computers are getting both smaller and packed more densely, the necessary cooling solutions become increasingly expensive. For instance, a cooling system for a 30.000 square feet, 10MW data center can cost \$2–\$5 million [71]. According to to the same source, every watt spent by computing equipment necessitates the consumption of an additional 0.5 to 1.0W operating the cooling infrastructure. This amounts to \$4–\$8 million in annual operating costs [76]. In data centers, where availability is essential, failures within the cooling infrastructure can be a major problem as this can result in reduced mean time between failure, and even service outages [64].

Towards the turn of the millennium, huge data centers started emerging across the globe. With as many as tens of thousands of servers [64], energy consumption again surfaced as a key design constraint. For some facilities the electricity expenses are one of the dominant costs of operating the DC, accounting for 10% of the total cost of ownership [49]. Although the rate at which power consumption in DCs increase is slowing down [48], trends of increased energy consumption in DCs are likely to continue.

Because of the vast number of computers currently employed in DCs, the economy of scale dictates that even small reductions in power expenditure on machine and device level can amount to large energy savings on data center scale.

At the machine level, clouds commonly employ hardware virtualization technologies to allow for higher degrees of utilization of the physical hardware. However, this approach is not without problems. The workloads encapsulated by virtual machines constantly compete for the available physical hardware resources of their host machines, and interference from this resource sharing can cause unpredictable performance. Even when virtual machine (VM) technologies are employed, some operating system (OS) will have to serve as a foundation, enabling the allocation of resources to the VMs. Virtual machine monitor (VMM) functionality is implemented as an extension to such an operating system.

The omni-kernel architecture (OKA) is a novel operating system architecture especially designed for pervasive monitoring and scheduling [52], [53]. The architecture ensures that all resource consumption is measured, that the resource consumption resulting from a scheduling decision is attributed to the correct activity, and that scheduling decisions are fine-grained.

Vortex [52], [53], [68], [69], [67] is an experimental implementation of the OKA providing a novel and light weight approach to virtualization. While many conventional VMMs expose virtualized device interfaces to its guest VMs [11], [78, p. 254–258], Vortex offers high-level commodity OS abstrac-

tions. Examples of such abstractions are files, memory mappings, network connections, processes, and threads. By doing this, Vortex aims to offload common OS functionality from its guest OSs, reducing both the resource footprint of a single VM and the duplication of functionality across all the VM OSs. Vortex does not currently provide a complete virtualization environment capable of hosting ports of commodity OSs. Instead, a light weight approach that targets compatibility at the application level is used; thin VM OSs similar to compatibility layers emulate the functionality of existing OSs, retaining their application binary interfaces (ABIs). Currently, a VM OS capable of running Linux applications such as Apache<sup>1</sup>, MySQL<sup>2</sup>, and Hadoop<sup>3</sup> exists [68], [69], while efforts to do the same for Windows applications are under way [36].

This thesis describes ROPE (Reducing the Omni-kernel Power Expenses), which introduces several dynamic power management algorithms to the Vortex implementation of the OKA.

#### 1.1 Problem Definition

This thesis shall design, deploy, and evaluate power management functionality within the Vortex operating system kernel. Focus will be to conserve energy while limiting performance degradation.

## 1.2 Scope and Limitations

Power management is a multifaceted problem. In the context of data centers, a multitude of approaches and techniques are currently being employed. In order to save as much energy as possible, all aspects of power consumption must be analyzed, understood, and managed cleverly. In this thesis, the focus lies on power management on a per-node basis. We do not focus on techniques involving multiple nodes, for instance through consolidation of virtual machines [55], [43], [81], intelligent placement of workloads [32], [64], or scheduling of work based on the availability of green power [10], [13]. Further, we do not focus on the use of exotic or mobile technology in order to save power [59], [34]. Rather, we specifically target software techniques for power management in standard enterprise blade servers.

- 1. http://httpd.apache.org/

- 2. http://www.mysql.com/

- 3. http://hadoop.apache.org/

#### 1.3 Interpretation

Our problem concerns effectuating PM while limiting performance degradations. If tradeoffs between energy savings and performance must be made, the evaluation of the implemented functionality should enable a user to make enlightened decisions. This requires that the system be tested with relevant benchmarks and workloads. Specifically, the implemented system should adhere to the following principles and requirements:

#### **Design Goals and Principles**

- **Simplicity:** Where possible, simple solutions should be adopted. This is especially important as Vortex is under continuous development by faculty and students.

- **Flexibility:** Flexibility is preferable over rigidity: Vortex is constantly changing. If ROPE is to remain relevant its implementation must be both flexible and robust.

- Orthogonality: ROPE should target the issues of energy efficiency along orthogonal axes. Solutions and policies should compliment rather than rely on each other, making future additions and modifications as uncomplicated as possible.

#### Requirements

- The system should reduce the power consumption of Vortex.

- The system should make use of existing standards for power management (PM) wherever possible.

- The implementation of the system should focus on performance. For all implemented functionality, performance implications should be evaluated.

## 1.4 Methodology

According to the final report of the ACM Task Force on the Core of Computer Science, the discipline of computing can be divided into three major paradigms. These paradigms are theory, abstraction, and design.

1.5 / CONTEXT 5

The first paradigm is *theory*. Rooted in mathematics, the theoretical approach is characterized by first defining problems, then proposing theorems, and finally seeking to prove them in order to determine potentially new relationships and make progress in computing.

Abstraction is rooted in the experimental scientific method. Following this approach one seeks to investigate a phenomenon by constructing a hypothesis, and then make models or perform simulations to challenge this hypothesis. Finally, the results are analyzed.

*Design* is the last paradigm, and is rooted in engineering. Within this paradigm, one seeks to construct a system for solving a given problem. First, the requirements and specifications of said system are defined. The system should then be designed and implemented according to these requirements and specifications. Upon completion of the system, it should be tested and evaluated.

For this thesis, the design paradigm seems to be the most fitting. We have stated a problem, its requirements, and specifications. Now, a prototype solving the problem according to the specification must be designed and implemented. The testing of the system will amount to quantitatively evaluating its performance and cost of operation.

### 1.5 Context

This project is written as a part of the Information Access Disruption (iAD) center. The iAD center focuses on research into fundamental concepts and structures for large-scale information access. The main focus areas are technologies related to sport, cloud computing, and analytic runtimes.

Specifically, this project is related to the Omni-kernel architecture project, where a novel OS architecture providing total control over resource allocation is under development. It is in Vortex, the current instantiation of this architecture, that ROPE has been implemented.

#### 1.6 Outline

**Chapter 2** covers some basics of power management, introduces some key concepts, and outlines often employed classes of PM algorithms. It also introduces different power management mechanisms.

- **Chapter 3** describes the architecture and design of ROPE, and how power management functionality have been introduced to the Vortex operating system kernel. Further, this chapter explains how different PM policies coexist and complement each other.

- **Chapter 4** covers the implementation specific details of the PM policies described in chapter 3. It also covers ACPI and how it is incorporated into the Vortex kernel. Intel-specific PM capabilities are also discussed.

- **Chapter 5** evaluates the power management policies implemented in ROPE, and contains our experiments and results.

- Chapter 6 presents related work.

- **Chapter 7** discuss some of our findings and results in greater detail, and covers how energy efficiency can be accommodated in the Omni-kernel architecture. Finally, it concludes this thesis.

# /2

# **Power Management**

This chapter covers the basic principles of power management (PM). First, key terms and concepts are introduced. Following this, different approaches to PM as well as common classes of algorithms are outlined.

## 2.1 Introduction to Power Management

Dynamic power management (DPM) [70], [19], [77] is a design methodology for dynamic configuration of systems, components, or software, that aims to minimize the power expenditure of these under the current workload, and constraints of service and performance levels requested by the user.

DPM can be applied by different techniques that selectively deactivate or power down components when they are idle or unexploited. The goal of all such techniques is to achieve more energy efficient computation, and a central concept of DPM is the ability to trade off performance for power savings in a controlled fashion while also taking the workload into account. The main function of a power management scheme, or policy, is to determine *when* to initiate transitions between component power states, and to decide *which* transitions to perform. For instance, if a device supports more than one PM state, one of these states may be more suitable to reduce energy consumption under a specific workload, than another. Consider, if the workload is memory bound, it might be possible to lower the frequency of a central processor unit

(CPU), thereby reducing power consumption, while still managing to perform all computations in a timely fashion.

Exactly what decision is (or should be) made at any time will be highly dependent on the active PM policy. Any performance constraints will play a fundamental role when making power management decisions [14], [70], regardless of whether the policy makes use of historical-, current-, or predicted future workloads to find the best course of action.

## 2.2 Evaluating Power Management Policies

Throughout this text, the term *workload*, as defined in [41], describes the physical usage of the system over time. This usage can be measured in any unit suitable as a metric. For instance, when implementing a policy that will power up or down a network interface card, average bandwidth and latency might be suitable metrics for capturing the characteristics of the workload. When deciding to spin down a hard drive, the number of read and write operations might be of more interest. Often, consecutive measurements of the workload characteristics are stored in a *trace*.

When attempting to conserve power by means of DPM policies, a problem that needs to be considered is the possibly detrimental effects of said policies on system performance. More precisely, it is desirable that the negative impact on metrics such as latency and job throughput is reduced to the extent possible [65], [70], [19], [77]. Because this is a critical issue, a means of comparing the amount of performance degradation of different policies or algorithms for dynamic power management is necessary. One way of approaching this is to define some baseline that different policies and algorithms can be compared to.

An important consideration of any power management system is that transitions between different power states of a device most often comes with a cost. If a transition is not instantaneous, and if the device is non-operational during this transition, performance can be lost when a transition is performed. Whenever transitions are non-instantaneous, there might also be a power cost associated with the transition. If the costs in performance, power, or both, are large, a power state might become close to useless as amortizing the transition costs becomes difficult [14].

Given a trace corresponding to some workload, an optimal baseline can be created in hindsight. Note that because no system can be all knowing of past, present, and future workloads, the optimal baseline can only be generated

offline. We define this optimal baseline, an *all knowing oracle*, as having the following characteristics:

- The device should not be powered down if this will affect performance negatively.

- The device should not change power states if the state transition will result in a reduction of saved power, i.e., the state transition will consume more power than is saved by entering the state and remaining in it throughout the idle period.

- The device should be powered down at all points in time not covered by the above cases, thereby maximizing the amount of saved power.

In [14], the authors survey several different approaches to DPM. We will adopt their notation when explaining applicability of dynamic power management. When switching a device into an inactive (sleep) state, this results in a period of inactivity. We denote the duration of a generic period at time n,  $T_n$ . This is the sum of the time spent in a state S, as well as the time spent transitioning into and out of the state. The break-even time for a given state, S, is denoted  $T_{BE,S}$ , and corresponds to the amount of time that must be spent in the state S in order to compensate for the power spent transitioning to and from it. Most often, lower power states have higher associated performance penalties. In the case that  $T_n < T_{BE,S}$ , there is typically not enough time to both enter and leave the inactive (sleep) state, or the time spent in the low-power state is not long enough to amortize the cost of transitioning to and from it. This means that if all idle periods corresponding to a given workload are shorter than  $T_{BE,S}$ , this power state can not be used to save any power. Transitions into a low-power state during an idle period that is shorter than the breakeven time for this state is guaranteed to waste energy. Because of this, it is often desirable to filter out idle times of very short duration [84].

$T_{BE}$  is the sum of two terms:  $T_{BE} = T_{TR} + P_{TR}$ . The first of these,  $T_{TR}$ , is the *total transition time*, meaning the time necessary to both enter and leave the low-power state. The second, *transition power* ( $P_{TR}$ ), is the time that must be spent in the low-power state to compensate for the power spent during the transition phases.  $T_{TR}$  and  $P_{TR}$  are given by equations 2.1 and 2.2.

$$T_{TR} = T_{\text{On,Off}} + T_{\text{Off,On}} \tag{2.1}$$

Where  $T_{\text{On,Off}}$  and  $T_{\text{Off,On}}$  are the times necessary to perform a transition from

the on- to the off-state, and from the off- to the on-state respectively.

$$P_{TR} = \frac{T_{\text{On,Off}} P_{\text{On,Off}} + T_{\text{Off,On}} P_{\text{Off,On}}}{T_{TR}}$$

(2.2)

Using equation 2.1 and 2.2,  $T_{BE}$  can be expressed in the following manner:

$$T_{BE} = \begin{cases} T_{TR} + T_{TR} \frac{P_{TR} - P_{\text{On}}}{P_{\text{On}} - P_{\text{Off}}} & \text{, if } P_{TR} > P_{\text{On}} \\ T_{TR} & \text{, if } P_{TR} \le P_{\text{On}} \end{cases}$$

(2.3)

Further, the energy saved by entering a state S for an idle period  $T_{\text{idle}}$ , with a duration longer than the break even time for this state,  $T_{BE,S}$  is given by the following equation:

$$E_S(T_{\text{idle}}) = (T_{\text{idle}} - T_{TR})(P_{\text{On}} - P_S) + T_{TR}(P_{\text{On}} - P_{TR})$$

(2.4)

In [35], the authors introduce two concepts useful when evaluating the quality of power management policies. The first of these—external measures—gives a quantitative measure of the interference between the PM policy and other applications. Any profit resulting from the use of the policy will also be quantified with external measures. Examples of metrics covered by external measures are power consumption, latency, and system resource consumption. Internal measures, on the other hand, can be used to quantify the accuracy of prediction algorithms. While the internal measures are useful when deciding on which prediction algorithms to use, the external measures are the ones that really matter for a running system.

## 2.3 Approaches to Power Management

In general, approaches to PM are either *heuristic* or *stochastic*. Although their goals are similar, the two classes of policies differ widely in their implementation as well as their theoretical foundations. Stochastic policies are theoretically optimal, and use statistical distributions to model workloads. Heuristic approaches, on the other hand, are not theoretically optimal, but often based on experimental results and practical engineering. Because of this, heuristic approaches such as static timeout policies—albeit often used with great

success—may lead to bad performance and unnecessary power consumption when the request rate for a service is highly variable [77].

PM policies can be further divided into discrete-time or event-driven variants. With discrete-time policies, decisions are re-evaluated at every time slice. Event-driven policies, on the other hand, only evaluate what action to take when some event, such as the arrival or completion of a request, occurs. The fact that discrete time solutions continuously re-evaluate the power settings of the system means that power is wasted if the device could otherwise be placed in a lower power state [84]. Further, PM policies can be split into stationary and non stationary policies. A stationary policy is constant in that it remains the same for all points in time, while a non stationary policy changes over time according to the experienced workload.

#### 2.3.1 Heuristic Power Management Policies

Heuristic PM algorithms can in broad terms be split into two classes: timeoutand rate-based. Common for all heuristic policies, is that results are not guaranteed to be optimal.

#### **Timeout-based Policies**

The most common heuristic policies are variants of timeout policies [84]. Whenever an idle period occurs, a timer is started. A state transition is initiated if the idle period is longer than some pre-defined timeout value. Timeout based policies have the disadvantage that they result in unnecessary power expenditure while waiting for the timeout to expire [85]. A static timeout based policy always employs the same timeout value, whereas adaptive timeout policies modify their timeout parameters in order to better meet some performance goal [35]. Simple adaptive policies can result in larger power savings for a given level of latency [39].

#### **Rate-based Policies**

With rate-based policies, some prediction unit or algorithm calculates an estimate (prediction) of future load for the power-managed device or system. Typical examples are estimation of idle periods [35], the number of incoming requests, or the bandwidth consumption of a webserver. Rate-based policies make the system or component perform a state transition as soon as an idle period begins, given that it is likely that the idle period will be long enough to save power [85]. The efficiency of an algorithm therefore depends on the

ability to estimate the duration of the idle periods to a satisfactory degree, as failure to do so can cause performance penalties and also result in waste of energy. Normally, thresholds are used to determine when to power a device up or down. Examples of rate-based predictors are different variants of moving averages.

#### 2.3.2 Stochastic Power Management Policies

Stochastic approaches to PM differ from heuristic techniques in that they guarantee optimal results as long as the system to be managed is modeled well enough [84]. All stochastic models use statistical distributions to describe the system that is to be power managed. For instance, while one distribution describes the time spent transitioning to and from different power states, another might describe the time spent by some resource to service a client's request, while a third might model the inter-arrival times of these requests. The distribution used to model the different parts of the system varies, and one typically tries to find a distribution that closely matches the real system. Although theoretically optimal, the quality of these models are highly dependent on the system being sufficiently well-modeled. Further, as the optimal solution is calculated from traces, the model quality will always be constrained by the trace quality, and the degree to which distributions fit the actual usage patterns [75].

#### 2.3.3 Machine Learning Based Power Management Policies

Machine learning revolves around the creation and study of computer systems and machines that can learn from data presented to them. Many examples of such systems exist, for example speech recognition systems, spam filters, and robot controlled cars. A formal definition of machine learning was presented by Tom M. Mitchell in his 1997 book on the topic:

A computer program is said to learn from experience E with respect to some class of tasks T and performance measure P, if its performance at tasks in T, as measured by P, improves with E. [60]

For example, a computer that learns to play a card game might improve its performance with regards to winning that game, as it gains experience by playing it against itself or others. The quality of machine learning systems are dependent on multiple design choices, such as which training data is used, the features extracted from this data, and the chosen algorithm for learning the target function based on the training data.

Machine learning has been used extensively in the context of PM. Examples include powering down idle hard drives and wireless network interfaces [28], [39], [86], putting CPUs to sleep and adjusting core frequencies [54], [9], [61], as well as energy efficient scheduling of tasks [93].

There are many possible ways to train a machine learning system. With *supervised learning*, pre-labeled training data is used to approximate the target function. The key point of supervised learning is that a human, for example some expert in the field of the classification problem, have to correctly label the training data so that it can be used to improve the performance of the algorithm. In contrast, *unsupervised learning* rely on the ability to uncover some hidden structure in raw unlabeled data. *Semi-supervised learning* combine these approaches. Labeled training data is used as an starting point for automatically labeling the remaining data. This has been found to improve learning accuracy considerably in some cases where the generation of a fully labeled training set is unfeasible, while unlabeled data can be obtained cheaply. *Reinforcement learning* is a category of machine learning algorithms that attempt to find ways of maximizing the reward (minimizing the cost) of a system by repeatedly selecting one among a set of predefined actions.

In the context of power management, machine learning approaches are often divided into two classes of systems, namely *pre-trained systems*, and systems employing *online learning*.

#### **Pre-trained Systems**

Pre-trained systems commonly employ supervised- or semi-supervised learning to train the employed PM algorithm. Typically, example workloads are used to obtain traces used for training. Unless a representative set of training workloads is used, the algorithm may become unable to generalize when experiencing real loads. Because of the dynamic nature of PM problems, pre-trained systems are less common than online ones. Nonetheless, pre-trained systems have been used successfully for PM, for instance to change CPU frequencies [9], [61], [47].

#### **Online Learning**

Online learning encompasses machine learning methods in which no set of separate training samples is used. Instead, the algorithm tries to produce the best prediction possible as examples arrive, starting with the first example that it receives. After making a prediction, the algorithm is told whether or not this prediction was correct, and uses this information to improve its prediction-

hypothesis. Each example-prediction pair is called a *trial*. The algorithm will continue to produce predictions as long as new examples arrive, and the learning and improvement of the hypothesis is thus continuous. Because the learning process never stops, it is sensible to employ an algorithm that is capable of computing successive prediction-hypotheses incrementally, and avoiding the potentially excessive costs of recalculating every hypothesis from scratch (thus having to store the examples indefinitely) [56], [57].

Online statistical machine learning has been used to control CPU frequency [45], while online reinforcement learning has been employed in the domain of energy efficient task scheduling and for managing wireless local area network (WLAN) interfaces [93], [86]. Online machine learning has also been used to spin down hard drives in order to conserve energy [39].

### 2.4 Power Management Mechanisms

PM can be performed on a wealth of devices. Notable examples are powering down network cards, spinning down hard drives, adjusting fan-speeds, etc. To enable software—for example an OS—to take advantage of available PM capabilities of the hardware, some mechanisms are necessary. First, it must be possible to detect the presence of any PM capable hardware. Second, the configuration of devices (and possibly the software itself) must be performed. Third, the software must have some method to communicate PM decisions to the hardware. The following sections gives a brief overview of different PM mechanisms. Thorough descriptions of these mechanisms are deferred to chapter 4.

#### 2.4.1 Device Detection and Configuration

With myriads of different hardware vendors and rapid technological development, the existence of multiple standards for detection and configuration of devices is not surprising. Examples are the use of vendor- and device-specific BIOS code, and advanced power management (APM) APIs and description tables. Advanced Configuration and Power Interface (ACPI) evolved from the need to combine and refine existing power management techniques such as those mentioned above, into a robust and well defined specification for device configuration and power management. Using this interface, an OS can manage any ACPI-compliant hardware in a simple and efficient manner.

### 2.4.2 Power Management of Devices

Through the use of for example ACPI, software can detect and configure PM capable devices in the system. ACPI provides information about devices through objects. While the objects normally contain tables of information, they can also contain methods that can be used to communicate software capabilities and initiate state transitions. Consider a PM-capable rotating hard drive drive: through ACPI it presents tables listing its power/performance states. Such tables would likely include the power consumption, bandwidth, and expected read/write latency for each state. Probably, it would also contain how long it takes to enter the different states, and their associated spin-up time—the time spent spinning the disk back up when leaving them. Now, using the information obtained from such tables, and ACPI accessible *methods* for the device, software can decide on what state the disk should reside in at any given time, and then make it enter the chosen state. Figure A.3 in appendix A illustrates the concepts described here, but for entry of CPU performance states.

Although ACPI provides a well defined and robust way of interacting with devices, not all devices support this specification. Legacy devices, and also relatively new hardware, can lack support for ACPI¹. Sometimes, such devices provide PM capabilities by means of some other specification or technology. Common examples are devices connected via PCI and PCIe interfaces, which define their own methods for performing PM. In addition, some specialized devices have functionality and properties not easily representable through ACPI. For instance, Intel employ both ACPI and their own custom mechanisms for detection, configuration, and power- and performance management of their CPUs [25], [26].

### 2.4.3 Power Management of CPUs

ACPI provides several mechanisms for controlling the power consumption and performance of CPUs. The two most commonly used (and the ones employed in this work) are power states (C-states), and performance states (P-states). C-states correspond to different CPU sleep-states, that is, states when no instructions can be executed and energy is conserved by powering down parts of the processor. P-states corresponds to combinations of CPU frequency and voltage, higher frequencies results in increased performance but also consume more power.

1. On our hardware, the Gbit NICs are PM capable but via PCI instead of ACPI. In fact, our entire platform is severely lacking in terms of ACPI support.

### **Dynamic Voltage Scaling**

Dynamic voltage scaling (DVS) enables software to dynamically adjust both the CPU voltage and frequency. Typical use of DVS can result in substantial power savings due to the dependency between CPU voltage, frequency, and power dissipation [40]. Consider, if implementing a chip using static CMOS gates, its switching power dissipation is given by equation 2.5, where P is the power, C is the capacitance being switched per clock cycle, V is the voltage, and f is the switching frequency.

$$P = CV^2 f (2.5)$$

As can be seen from equation 2.5, power dissipation is quadratically proportional to the CPU voltage<sup>2</sup>. Because of this, the frequency of the CPU must be reduced when lowering the operating voltage in order to save power. As such, DVS trades performance for energy reductions. In modern CPUs, a set of *frequency/voltage pairs* are often exposed through technologies such as Enhanced Intel<sup>®</sup> SpeedStep<sup>®</sup> [27], or AMDs Cool 'n' Quiet™/PowerNow!™[20], [21]. These technologies simplify power management, and ensure that the paired frequencies and voltages are compatible. For this reason, DVS is often also called dynamic voltage and frequency scaling.

<sup>2.</sup> For a relatively non-theoretical explanation as to why is this is the case, the following blog posts can be recommended:

http://software.intel.com/en-us/blogs/2009/o6/29/why-p-scales-as-cv2f-is-so-obvious http://software.intel.com/en-us/blogs/2009/o8/25/why-p-scales-as-cv2f-is-so-obvious-pt-2-2

## /3

### ROPE Architecture and Design

This chapter covers the architecture and design of ROPE, which contains all PM functionality in Vortex. First, the architectural foundations and basic ideas are established. Following this, designs for various PM policies are introduced and discussed in more detail.

### 3.1 ROPE Power Management Architecture

Power management (PM) of the CPU is critical for saving power. Despite modern CPUs having become considerably more energy efficient in recent years [12], the CPU is still responsible for 25%–60% of the total power consumption of computers [59], [88], [12]. To reduce power consumption, the CPU must be managed with regards to both power- and performance states. In broader terms, this means putting the CPU to sleep and adjusting its frequency.

ROPE introduces PM functionality to the Vortex kernel. In ROPE, management of power- and performance states (C- and P-states, respectively) is performed independently of each other. The architecture of ROPE is founded on two central concepts; *policies*: rules describing the use of power- and performance states; and *enforcement*: effectuating the policy with hardware. As

outlined in section 2.1, different policies can vary significantly in their nature, i.e. they can be static or dynamic, pre-configured or based on runtime metrics. Thus, they may rely on different data structures, libraries, instrumentation<sup>1</sup>, etc. Further, different policies might share method of enforcement. For instance, a set of timeout-based policies, each with a distinct timeout value, can rely on the same method for enforcing the timeout, while a more complex policy might need a completely different enforcement.

The design goals for ROPE include simplicity and flexibility. Guided by these, we base the architecture and design of our solutions on the basic ideas of policies and enforcers. An OS kernel is a delicate and complex piece of software, and our solutions are influenced by this environment. The necessary logic, instrumentation, and data structures, must often be incorporated into the Vortex kernel in a scattered and fragmented fashion, leveraging existing code paths and infrastructure. Based on these observations, we deem it appropriate *not* to establish any kind of rigid framework for the implementation of our PM functionality, as such a framework may quickly become an impediment with regards to flexibility. Figure 3.1 outlines the described architecture.

### 3.2 Design

This section describes several different designs of PM policies. Some of these provide alternative solutions to the same problem, while other policies have different objectives. Policies with different objectives are intended to complement each other, augmenting the Vortex PM system as a whole. Although all CPU PM features will be somewhat intertwined, we propose policies along three orthogonal axes:

- **CPU power state management:** These policies control when to turn a CPU-core off, and what to do when it is not executing instructions, e.g. which CPU C-state to enter.

- **CPU performance state management:** These are policies governing the performance of the CPU core when it is powered on. Typically, this means selecting one of the available CPU P-states.

- Energy efficient scheduling: When the individual CPU cores are powered down and clocked according to the workload, it becomes interesting to avoid unnecessary wake-ups. Using energy efficient scheduling,

- For example hardware instrumentation using performance monitoring counters (PMCs), or software states.

3.2 / DESIGN 19

**Figure 3.1:** Architecture of PM functionality implemented in Vortex.

it is possible to assign tasks to cores such that as many cores as possible are kept inactive, and thus sleeping, at any given time.

A single PM policy is realized through an enforcement mechanism (EM), and the structures and logic necessary to support this EM. These auxiliary structures and pieces of logic provide the EM with necessary information when effectuating PM decisions. Examples of such information could be how long the CPU must remain idle before entering a given C-state, which C-state to enter, and so on. We treat this logic, its data structures, and the information it contains, as a black box, and call it a Policy State Manager (PSM). As long as the PSM is paired with its matching EM, the policy implemented by the two will be effectuated, and the rest of the Vortex kernel will remain entirely independent from the introduced PM policy.

Modern CPUs commonly provide the possibility of adjusting the voltage and frequency of sub-components, or voltage/frequency islands (VFIs) within a single chip. For example, recent AMD Opteron processors support independent frequency control of all four cores, the shared L3 cache and on-chip northbridge, the DDR interface, and four HyperTransport links [46], [40]. In accordance with this trend, all PM functionality implemented in ROPE oper-

ates at a per-core level. This design choice results in a high degree of flexibility, which is especially desirable in the context of a VMM. For example, in the current version of the Vortex kernel all interrupts related to network traffic are handled by a single CPU core<sup>2</sup>. For some application scenarios, it might be necessary to ensure maximum performance with regards to network latency. With the per-core PM approach, a less aggressive policy<sup>3</sup> can be configured for the core handling the network traffic. Further, different tenants can be configured to run on separate cores, which in turn are configured to use a PM policy matching the customer's desired performance/carbon footprint.

The complexity of different PSMs will vary with the policies they support. In the following paragraphs, different PM policies available in Vortex are described. Some of these are relatively straight-forward and have very simple PSMs, while others are more sophisticated.

### 3.2.1 CPU Core Power State Management

ROPE supports three different policies for managing CPU C-states. This section covers their design.

### **Aggressive Entry of C-states**

The simplest PM policy in Vortex is to enter a given C-state aggressively whenever a core is idle. With this policy, the enforcer simply needs to know *which* C-state to enter, and then execute a state transition. The design for this policy is illustrated in figure 3.2.

### **Static Timeout based C-state Entry**

With static timeout-based policies, a constant timeout value is used to determine whether or not a C-state should be entered. The device being managed has to remain inactive throughout the duration of the timeout for the low power state to be entered. In this policy, the PSM is responsible for providing the static timeout value to the enforcement module. Figure 3.3 illustrates the

- 2. Using only a single core for handling network interrupts is a configuration choice. On the current hardware, it is most performance inducive that the same core both insert packets into the transmit queue, and remove packets from the receive queue. This is because both of these queues are protected by the same lock, and using a single core thus avoids lock contention. Experiments have shown a 5.5% increase in CPU consumption if more than one core is used [52].

- 3. PM could even be deactivated for this core all together.

3.2 / DESIGN 21

Figure 3.2: Design of a policy that aggressively enters C-states.

overall design of this solution.

**Figure 3.3:** Design of a policy for entering a C-state following a static timeout.

### **Select Best Performing C-state**

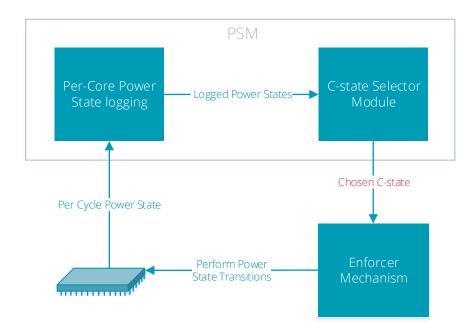

This policy employs an algorithm that dynamically selects which C-state to enter at runtime. This is done at the granularity of individual CPU-cores. The PSM for this policy is composed of two main sub-components, each serving a distinct purpose:

- **Power state logger:** Performs runtime logging of the current power state of a CPU-core.

- **C-state selection module:** Calculates the power saved and latency added as a result of aggressively entering different C-states. Based on these calculations, the currently best performing C-state is chosen.

Figure 3.4 illustrates the design of the policy where the best performing C-state is selected.

**Figure 3.4:** The design of a policy where the best performing C-state is chosen.

### 3.2.2 CPU Core Performance State Management

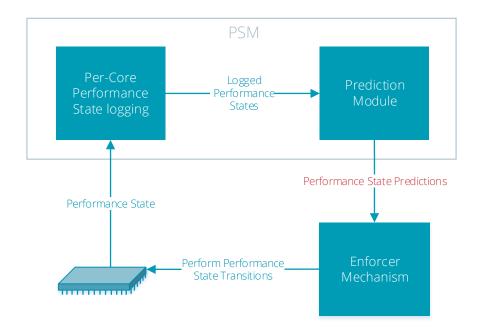

While the previous section outlined different policies for conserving energy using CPU C-states, this section considers the design of a policies for controlling *performance* states on a per-core basis. These policies and their components are responsible for adjusting the operating frequency of an individual core according to the workload. We employ two workload prediction techniques for selecting which P-state to use at any given time, both of which share the same general design.

The PSM for supporting dynamic selection of P-states consists of two key components: a *Performance State Logger* and a *Prediction Module*. Figure 3.5 illustrates the design of our P-state management solution.

- **Performance state logger:** Performs runtime logging of the current performance state of a CPU-core.

- **Prediction module:** Generates predictions about which P-state to use. Relies on records of previously experienced workload patterns in order to make these predictions.

3.2 / DESIGN 23

Figure 3.5: The design of a policy capable of managing CPU performance states.

### 3.2.3 Energy Efficient Scheduling

The third and final branch of PM algorithms implemented in ROPE is that of energy efficient scheduling. In essence, this problems boils down to keeping the maximum number of cores idle for as long as possible. There are several issues that must be considered when designing an energy efficient scheduling solution:

- Multiple cores per chip: Modern CPUs often have multiple cores per chip, or *package*. Although some CPUs, such as the previously mentioned AMD Opteron, feature voltage/frequency islands (VFIs) per core, many do not. On our platform, all cores on a package share the circuitry providing the voltage. This means that the voltage must be maintained at a level corresponding to the needs of the most voltage-hungry core on the chip. If the maximum amount of power is to be saved, the CPUtopology must be taken into account. For example, under light load, maximum power savings can be achieved when all the cores in a physical package are completely loaded before distributing the load to another idle package [83].

- Cache warmness: To keep caches warm, it is undesirable to unneces-

sarily move threads between CPU-cores. This results in an interesting tradeoff: distribute the total load evenly to all active cores, making sure that the lowest possible voltage can be drawn; or optimize for cache warmness and performance, risking that a single core increases the voltage requirements of the entire package.

• Cache Contention: Although maximum power savings can be achieved by loading a single package as much as possible before recruiting an inactive one, this can lead to suboptimal performance. The reason for this is that cores on the same package often share lower level caches. If many threads are scheduled on the same package, contention for these shared resources will occur. The performance impact of this will be highly dependent on the behavior of the scheduled tasks: if the tasks are not memory or cache intensive, performance impact will be minimal [83].

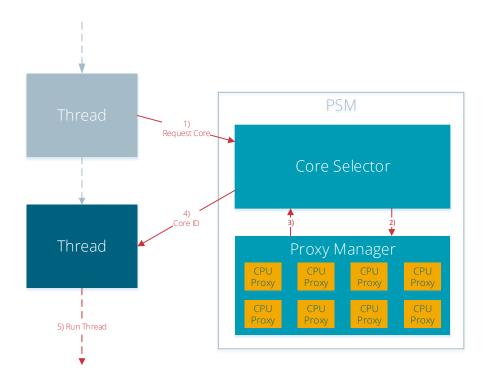

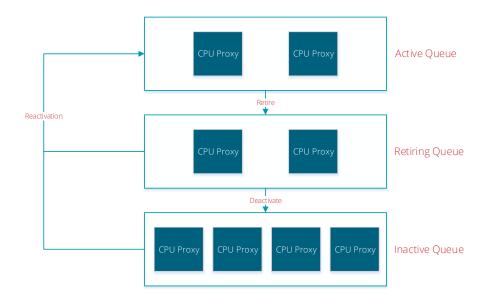

We do not wish to break our design principle of orthogonality, and have our energy efficient scheduler directly alter the C- or P-states of the different cores. This would certainly complicate the coexistence with existing policies managing CPU-states. Instead, we opt for an design where the scheduler is decoupled from the hardware, and attempts to save power while working with abstract *proxies* of the physical CPU-cores. A *Core Selector* implements a scheduling policy while interacting with a *Proxy Manager*. The Proxy Manager holds the state of the physical CPU-cores, such as their current utilization, whether they are active or sleeping, and so on. Together, these components constitute the PSM. This PSM is hooked directly into the existing scheduling framework of Vortex, which serves as the EM. This design is illustrated in figure 3.6.

3.2 / DESIGN 25

Figure 3.6: Design of an energy efficient scheduler.

## /4

### **Implementation**

In this chapter, we describe the implementation of several PM policies along the three orthogonal axes of C-states, P-states, and energy efficient scheduling. First, we describe some of the mechanisms that are used in ROPE to control the hardware. We then explain a online machine learning algorithm used in one of our P-state predictors. Lastly, we describe the implementation of each of the PM policies available in ROPE, and provide insights into the costs of operating these.

### 4.1 ACPI

ACPI is a method of describing hardware interfaces in a terms abstract enough to allow flexible hardware implementations, while being concrete enough to allow standardized software to interact with such hardware interfaces [22]. The ACPI specification was created to establish common interfaces that enable robust OS-directed motherboard device configuration, and power management of devices and systems. ACPI is a fundamental component for Operating System-directed Power Management (OSPM).

ACPI evolved from the need to combine and refine existing power management BIOS code, advanced power management (APM) APIs, and description tables, etc., into a robust and well-defined specification for device configuration and power management. Using an ACPI-specified interface, an OS can

manage any ACPI-compliant hardware in a simple and efficient manner.

At the heart of the ACPI specification are the ACPI System Description Tables. These describe a specific platform's hardware, and the role of ACPI firmware is primarily to supply these ACPI tables (rather than a native instruction API) to PM software [22]. The System Description Tables describe the interfaces to the hardware, and some of these tables include "definition blocks" that contain ACPI Machine Language (AML): an interpreted, and abstract machine language. Using this language, hardware vendors can describe their hardware—certain that any ACPI-capable OS can interpret it correctly. The ACPI System Firmware, in addition to supplying description tables, also implements interfaces that can be used by the OS. For example, if the description tables contain an ACPI-object for restarting a device, this object (which the OS can interact with) will be backed by firmware that controls the actual hardware.

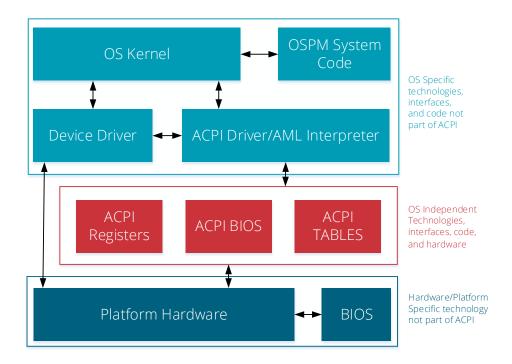

Figure 4.1 shows the architecture of ACPI. ACPI itself (shown in red) is independent of both the underlying hardware and the OS. Any OS that wishes to support ACPI must provide drivers, and a AML parser- and interpreter. If these components are in place, any interfaces and information presented by the platform can be accessed and used. Similarly, the hardware is not a part of ACPI per se. However, if the hardware wishes to expose functionality to the OS, it can do so through ACPI-objects accessible through the ACPI system description tables.

### 4.1.1 Supporting ACPI in Vortex

The ACPI standard consists of multiple components that allow the setup and power management of various devices. These components include ACPI name-space management, ACPI table and device support, ACPI event handling capabilities, and AML parser/interpreter functionality. The ACPI Component Architecture (ACPICA), developed by Intel Corporation, defines and implements these software components in an open-source package. One of the major goals of this architecture is to isolate the operating system from the code necessary to support ACPI. Most of the ACPICA code base is independent of the host OS in which it exists, using only a thin translation layer to access necessary OS functionality. To port ACPICA to a new operating system, only this OS specific layer must be implemented. This is necessary because every operating system is different, and the way an OS provides necessary services such as synchronization, input/output, or memory allocation, can differ enormously [24].

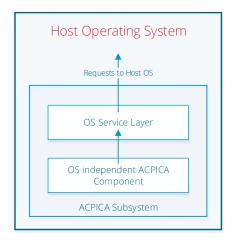

The ACPICA subsystem resides within the OS, and all interaction between

4.1 / ACPI 29

Figure 4.1: Architecture of ACPI.

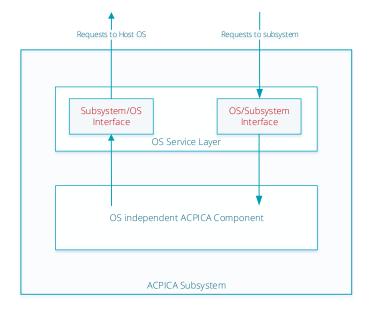

the host operating system and the OS-independent ACPICA components is performed through the thin service layer. This is illustrated in figure 4.2. In our case, the OS Service Layer (OSL) is implemented with approximately 1000 lines of Vortex-specific C code.

The OSL consists of two interfaces. These interfaces are used to support access to the host OS functionality as explained above, but also allow the host OS access to the functionality of the ACPICA subsystem, for example setup and power management of devices. A sketch of this can be seen in figure 4.3.

### 4.1.2 CPU Performance and Power Management using ACPI

ACPI provides three mechanisms for controlling the performance states of processors. These are:

- Processor power states, named Co, C1, C2, ..., C<sub>n</sub>.

- Processor clock throttling.

**Figure 4.2:** The figure illustrates how the ACPICA-subsystem resides within and interacts with the host operating system.

**Figure 4.3:** The figure illustrates how the operating system service layer of the ACPICA subsystem is structured into two interfaces, together facilitating the necessary bindings between the subsystem and the host OS.

4.1 / ACPI 31

• Processor performance states, named Po, P1, P2, ...,  $P_n$ .

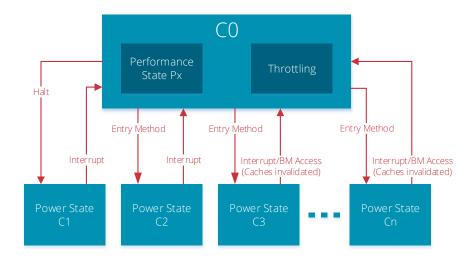

If supported by the platform, the OS can use these mechanisms to save power while attempting to meet performance constraints. Central to managing both performance and power are the processor power states. These states, denoted Co through  $C_n$ , are used conserve power by halting the execution and shutting down internal processor components. The Co state is the only active state (where execution occurs), and all other power states (from C<sub>1</sub> up to C<sub>n</sub>) are sleep states. While in a sleep state, the processor is unable to execute instructions. Higher-numbered sleep states conserve more energy. Each sleep state also has an associated entry and exit latency, which also typically increases with energy savings. All processors that meet ACPI standards must support the C1 state (which corresponds to the HLT instruction), whereas all other processor power states are optional. Further, the C1 (and C2 if supported) state rely on the platform maintaining state and keeping caches coherent. In addition, the latency of the C1 state must be kept sufficiently low that "OSPM does not consider the latency aspect of the state when deciding whether to use it" [22]. Aside from putting the processor in a lower power state, entering C1 should have no software-visible consequences. The same goes for the optional C2 state, differing only from the C1 state by its higher latency and greater energy savings. The even deeper sleep states—C3 and beyond—rely on the OS to maintain cache coherency, for example by flushing and invalidating the caches before entering the C<sub>3</sub> state. When in the Co power state, the use of throttling and processor performance states enables fine grained control of performance and energy expenditure.

The relationship between processor power- and performance states, as well as clock throttling is illustrated in figure 4.4. While in the Co state, CPU P-states and clock throttling can be used to adjust the performance level. From CO, C1– $C_n$  can be entered using entry methods defined in ACPI objects. Note that the C1 state is available through the HLT instruction. When in a sleep state, Co can again be entered if an interrupt occurs, or for higher-numbered C-states, in the occurrence of a busmaster access.

Processor performance states are—as their name implies—used to adjust the performance of a processing unit. As they all allow execution of instructions, they reside within the Co power state. The performance states are named Po through  $P_n$ , where Po is the state offering the highest level of performance. As with C-states, a variable latency is associated with entering and exiting a P-state. P-states offer OSPM the opportunity to alter the operating frequency for the processor. For instance, the Intel Xeon x5355 processors offers three P-states (Po, P1, and P2), at 2.66, 2.33, and 1.99GHz respectively.

**Figure 4.4:** The figure illustrates how the processor power- and performance states, as well as throttling capabilities are organized. This figure is loosely based on figure 8-39 of the ACPI specification version 5.0.

To facilitate the above mentioned functionality, a myriad of different ACPI objects must be presented by the platform and used by the software implementing OSPM. Appendix A gives a brief introduction to some of the most essential of these objects.

### 4.2 Intel Specific Advanced Power Management